近日,YouTube 上一段从零开始造 CPU 的视频走红。博主名叫 Robert Elder,来自加拿大,擅长软件咨询与开发,目前成立了自己的软件公司。在视频中,Elder 展示了他从零开始造 CPU 的全部过程。

具体来说,整个过程总共分为 19 步:

- 找到一块石头。

- 把石头砸碎,获得 98% 的浓缩二氧化硅。

- 将其纯化为 99.9% 纯二氧化硅。

- 进一步提纯至 99.9999999% 的多晶硅金属。

- 将多晶硅锭放入坩埚中。

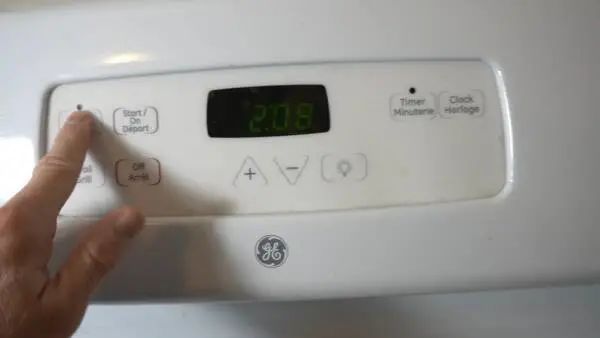

- 将硅锭加热至 1698 °K(约 1424.85℃)。

- 加入结晶种料。取一小块单晶硅作为结晶种料浸入熔融硅的大桶中。

- 待晶体冷却后慢慢将其拉出,获得纯硅单晶。

- 把纯硅单晶切成薄片。

- 用硼、磷或其他掺杂剂掺杂晶片。

- 在晶圆上涂上光刻胶。

- 取一个带有所需电路图案的铬蚀刻光刻石英掩模,并用激光束照射它以将电路图案投影到晶片上。

- 曝光显影。光罩产生的阴影位置将控制光刻胶在硅片表面发生化学变化的位置(取决于您使用的是正性还是负性光刻胶)。

- 显影光刻胶。

- 腐蚀晶片的暴露部分。

- 执行无数次同质外延、异质外延、伪外延、扩散掺杂、铜互连层、化学机械抛光、光刻胶应用、酸蚀刻和光掩模曝光的迭代和重复,以在晶片上建立所需的特征。

- 芯片切割,获得未封装的硅芯片。

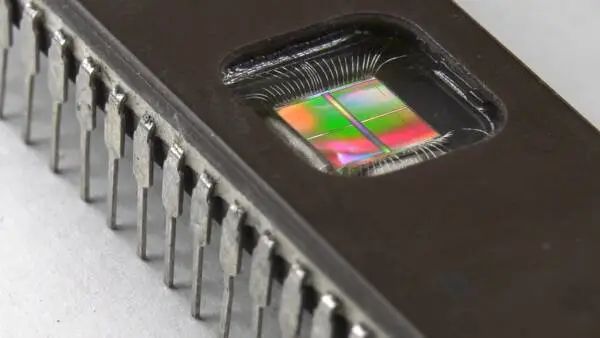

- 找到硅芯片上的焊盘,并连接键合线,或者像现在大多数现代处理器那样使用倒装芯片方法。

- 芯片封装。使用焊线或焊球在芯片封装上的引脚和硅片上的焊盘之间提供电气连接。

以上就是制作 CPU 的完整步骤。

不过 Elder 表示,现代 CPU 的制造过程远比他所描述的更复杂,也更不明确,每一代新一代芯片通常都会改变在晶圆上构建特征的方式(不仅仅是在特征尺寸方面)。他在制作 CPU 的过程中也省略了很多重要的步骤和细节,比如光阻剂和显影液精确的的化学成分 / 浓度、在晶圆上构建特征的方式。

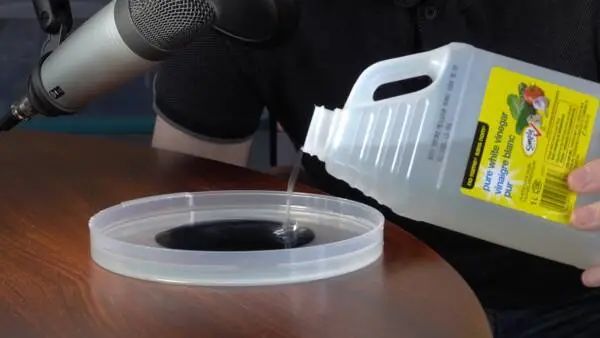

同时,Elder 还提醒大家,他在视频中使用的“光刻胶”和“显影剂”只是彩色道具,真的化学品相当危险,只能在通风良好的区域或通风橱中,并且使用适当的安全装置,才能使用它们。

Elder 表示,虽然业余爱好者不太可能自己造出尖端的纳米级芯片,但微米级的还是可行的。并且 YouTube 上另一博主 Sam Zeloof 确实试过。“如果你的光学系统正确的话,我认为你甚至可以用比他少得多的设备来制造一些基本的芯片”,Elder 在视频中提到。

Elder 提到的 Sam Zeloof 堪称天才少年。

2018 年,高三的 Sam Zeloof 在车库里制造了自己的第一代 Z1 芯片,该芯片只包含 6 个晶体管,属于一块纯粹的制程与设备测试芯片。今年大四的他,在掌握了更多芯片知识与工艺技能之后,做出了更进一步的尝试。这一次的 Z2 计划在 10 微米多晶硅栅极制程上容纳 100 个晶体管,这样的晶体管密度设计与英特尔推出的第一款处理器完全相同。

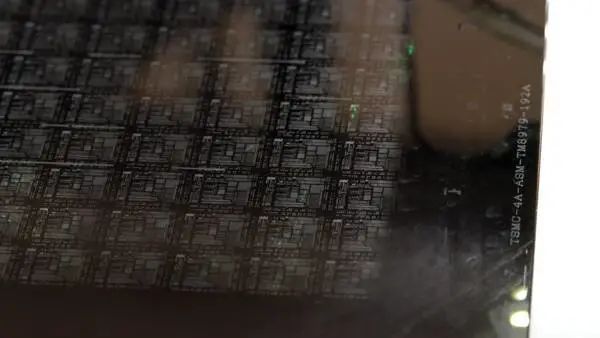

这块芯片包含一个简单的 10 x 10 晶体管阵列,用于测试、表征及调整制程,也作为迈向更先进 DIY 计算机芯片的重要一步。当初的英特尔 4004 包含 2200 个晶体管,而 Sam Zeloof 现在已经能够在同一块芯片上布设 1200 个晶体管。

这块芯片很小,大约是上一块芯片面积(2.4 平方毫米)的四分之一,所以检测工作很难进行。而每块芯片上都有一个简单的 10 x 10 N 沟槽 FET 阵列,可以为 Sam Zeloof 提供大量特性数据。因为设计非常简单,所以 Sam Zeloof 直接用 Photoshop 就完成了布局设置。每列 10 个晶体管共享一个公共栅极连接,每行与相信的晶体管串联在一起,共享同一源极 / 漏极端子。整个结构类似于 NAND 冷艳,但他这么设计只是为了让金属焊盘能足够大,降低探测难度。换句话说,如果每个 FET 都对应 3 个焊盘,那尺寸就太小了。

下图所示,为一个 10 微米 NMOS 晶体管,金属层上有轻微的未对准痕迹(左侧有一部分触点未能覆盖)。红线部分为多晶硅,蓝色则是源 / 漏栅极。

单 NMOS 晶体管

单 NMOS 晶体管到这里,Sam Zeloof 已经制作出一款运算放大器(Z1)与一个类似于内存的阵列(Z2)。尽管晶体管密度极低,但整个项目仍然非常有趣。具体制程还需要一点调整,但现在已经能够以稳定的方式制造高质量晶体管,接下来也应该可以设计出更复杂的数字与模拟电路。每个芯片的测试工作非常乏味,所以 Sam Zeloof 还打算自动化完成测试流程,并在成功后发布更多数据。

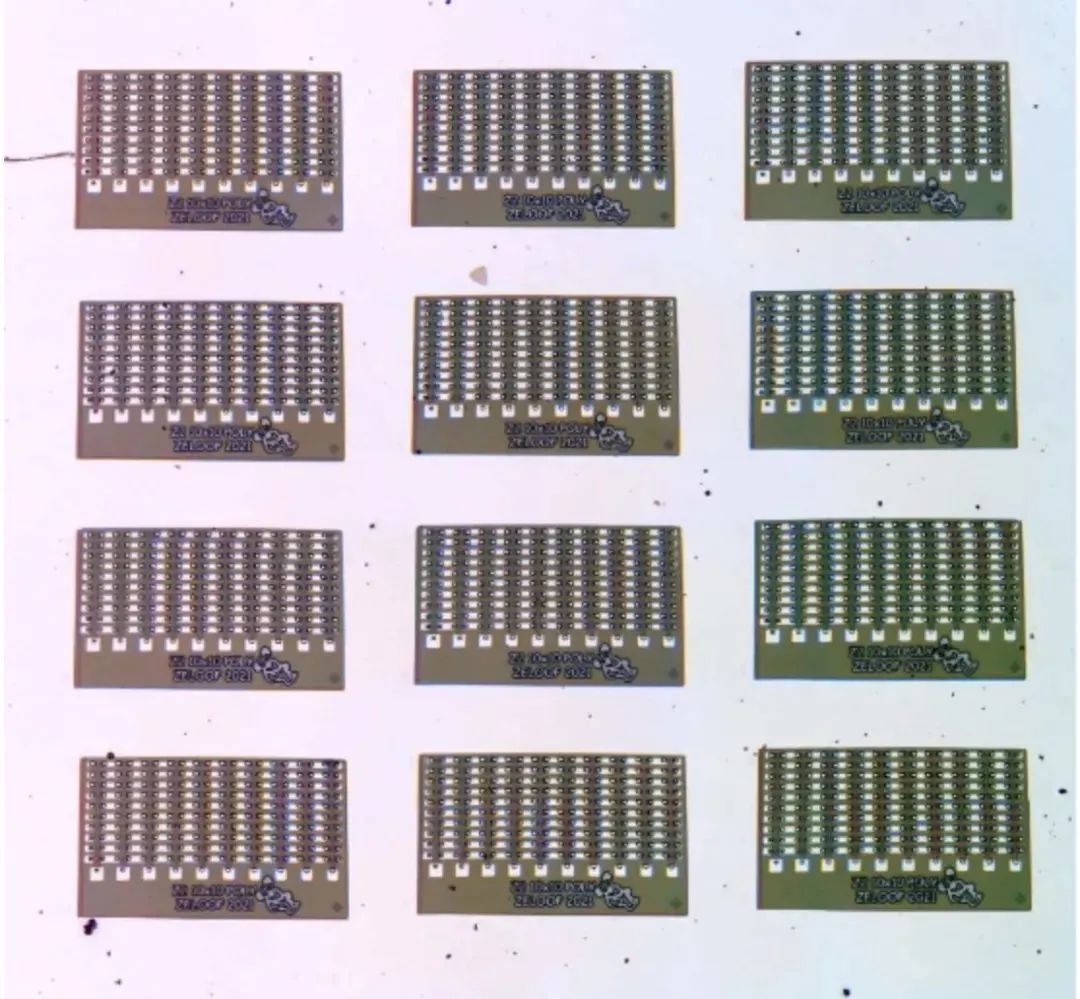

Sam Zeloof 已经制作了 15 个芯片(共 1500 个晶体管),而且其中至少有一个芯片实现了“功能完备”,至少两个芯片能实现“基本功能”—— 即至少约 80% 的晶体管能够正常工作。但目前 Z2 的产量数据还不乐观,最常见的缺陷出现在源或漏栅极同主体硅沟槽之间的短路上。顺带一提,Z1 的主要缺陷集中在栅极漏电或短路上。

有关 Z2 的“先栅极” 工艺可以阅读 Sam Zeloof 的博客:http://sam.zeloof.xyz/

在 Sam Zeloof 的博客中写道:整个制程工艺还有不少改进的空间,特别是应该与 CMOS 相兼容;但目前的方案至少简化了制造流程,也把必要工具控制在最低限度。

在理想情况下,1 微米厚的介电层(橙色)应该使用 CVD SiO2(可以在家中加工的 TEOS 氧化物),但我实际使用的是光刻胶。大多数光刻胶能够在 250°C 左右的烘烤下形成坚硬的永久介电层,可以直接替代 CVD 或 PECVD 氧化物。当然,这里也可以使用旋制氧化硅 / 溶胶凝胶。SiO2 蚀刻则是在由除锈剂或 RIE 制成的缓冲 HF 溶液中完成的。

下面就是拼合之后的晶片整体图了:

虽然还和先进的现代技术生产出来的芯片存在一定差距,但 Robert Elder 和 Sam Zeloof 向我们证明了,普通人也有徒手造芯片的可能。在芯片短缺的当下,如果有更多像他们一样充满创造力、想象力和动手能力,或许芯片危机也将迎来改变。

![]()